# A 0.5V-V<sub>IN</sub>, 0.29ps-Transient-FOM, and Sub-2mV-Accuracy **Adaptive-Sampling Digital LDO Using Single-VCO-Based Edge-Racing Time Quantizer**

Jeonghyun Lee, Jooeun Bang, Younghyun Lim, Seyeon Yoo and Jaehyouk Choi Korea Advanced Institute of Science And Technology (KAIST), Daejeon

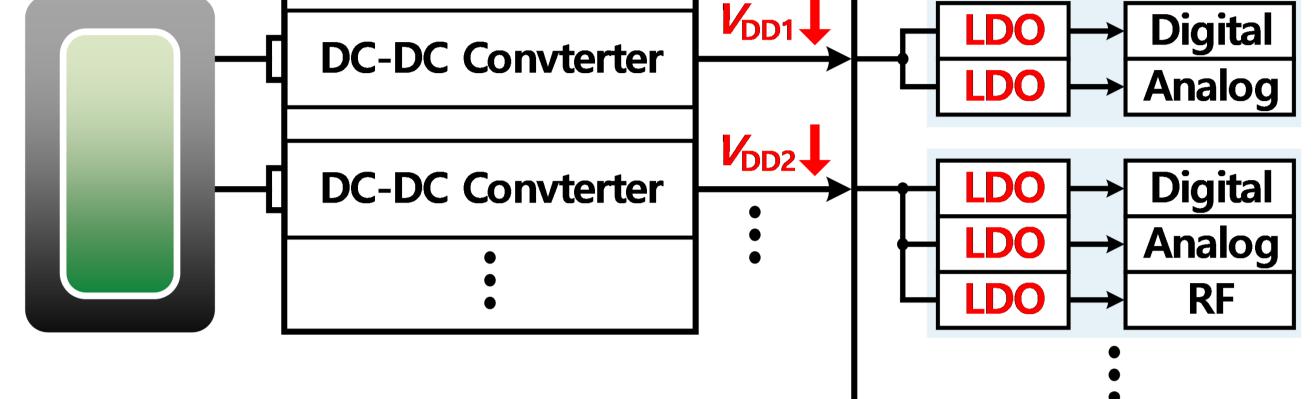

|         | Motiva | ation             | <b>Problems of Prior Architectures</b>                                    |  |  |

|---------|--------|-------------------|---------------------------------------------------------------------------|--|--|

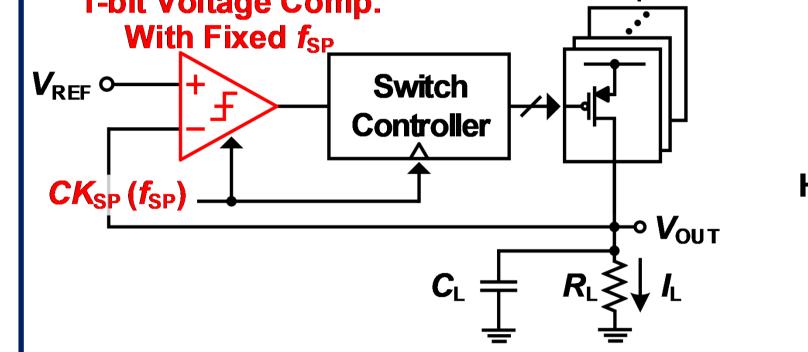

| Battery | PMIC   | <b>Mobile SoC</b> | Digital LDO Using Voltage Comparator [3]: Trade-off btw Power & Transient |  |  |

|         |        |                   | 1-bit Voltage Comp.<br>$M_{PS} = Low f_{SP}$                              |  |  |

- DC-DC converter providing supply voltages w/ high efficiency

- LDO regulating the supply voltages to optimal levels

- **Dynamic**  $V_{DD}$ -scaling, popular to save power - Needs of providing ultra-low  $V_{DD}$ s in an efficient way

- **Demanding reliable operation of LDOs under ultra-low V**<sub>DD</sub>

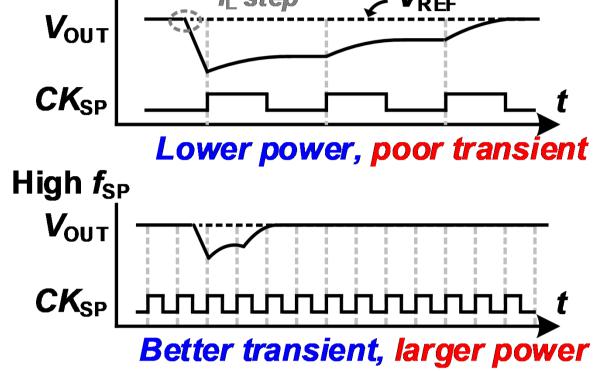

Digital LDO Using Multi-bit ADC [2]: Trade-off btw Power & Accuracy

## **Concept of Proposed Idea**

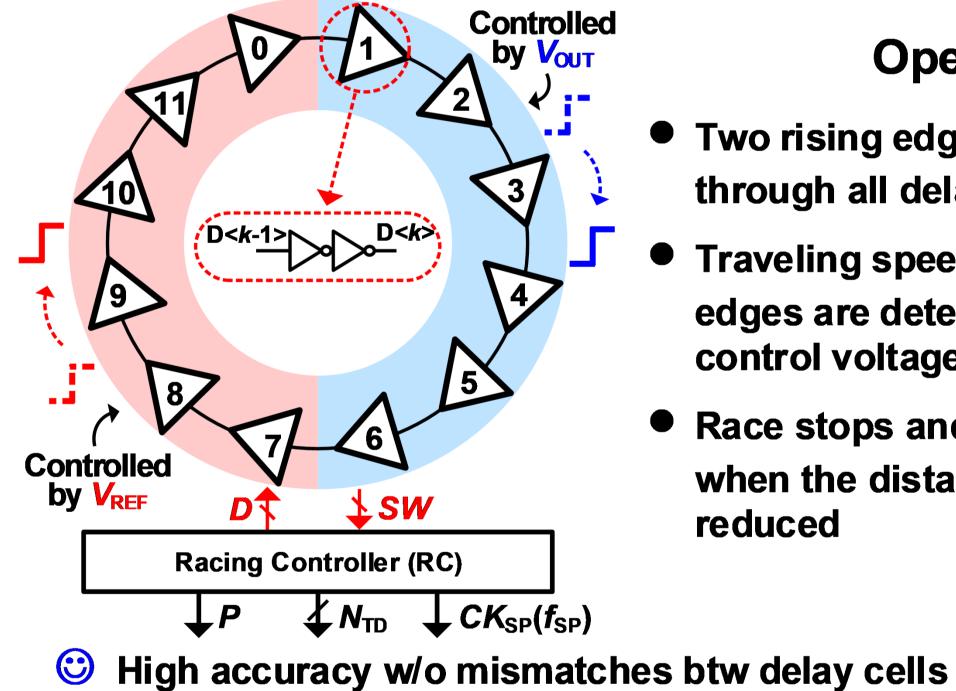

Single-VCO-Based Edge-Racing(SVER) Time Quantizer

Operation

## Architecture of Proposed DLDO

- Two rising edges equally passing through all delay cells

- Traveling speed of the two rising edges are determined by different control voltages, V<sub>OUT</sub> & V<sub>REF</sub>

- Race stops and decision made, when the distance between two edges

- Magnitude and polarity of voltage difference

- Very high maximum  $f_{SP}$  available  $\rightarrow max(f_{SP}) = N/2 * max(f_{REF}, f_{OUT})$  $\bigcirc$

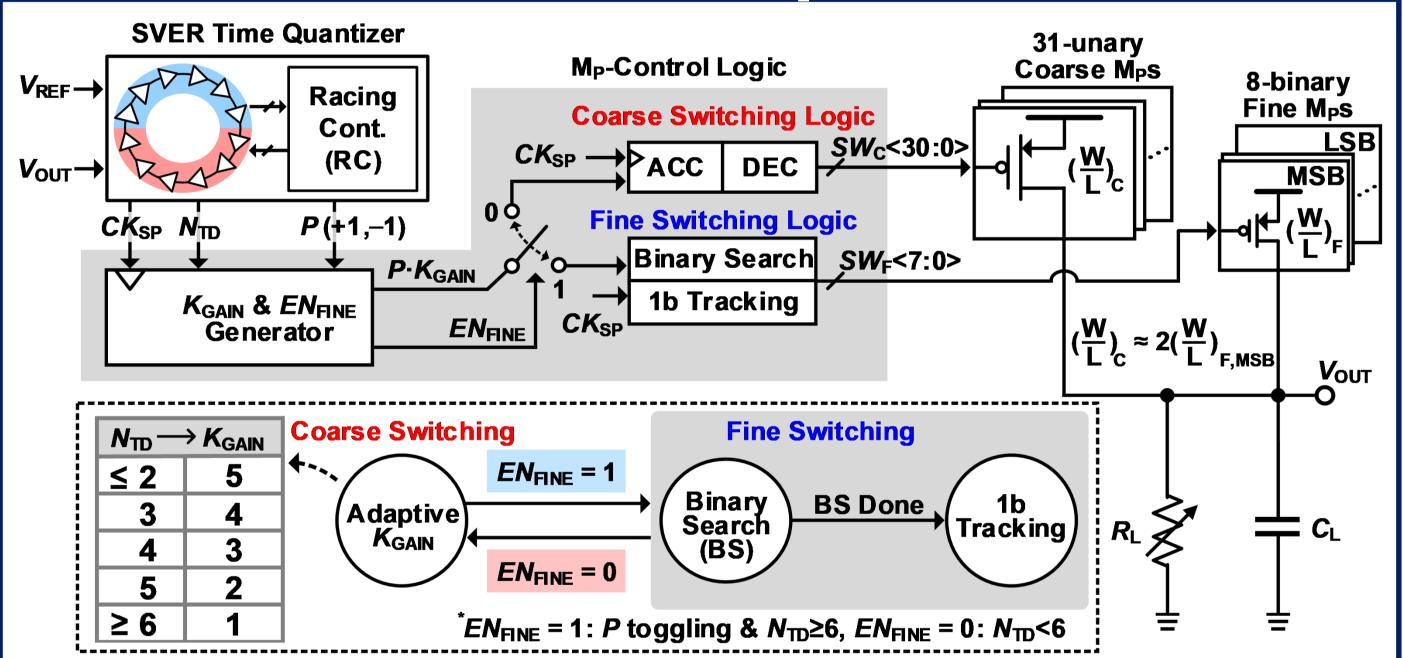

- SVER time quantizer compares  $V_{OUT}$  with  $V_{REF}$ , and delivers the information of the racing result to the MP-Control Logic

- The MP-Control Logic controls the switches of the coarse and the fine pass transistors

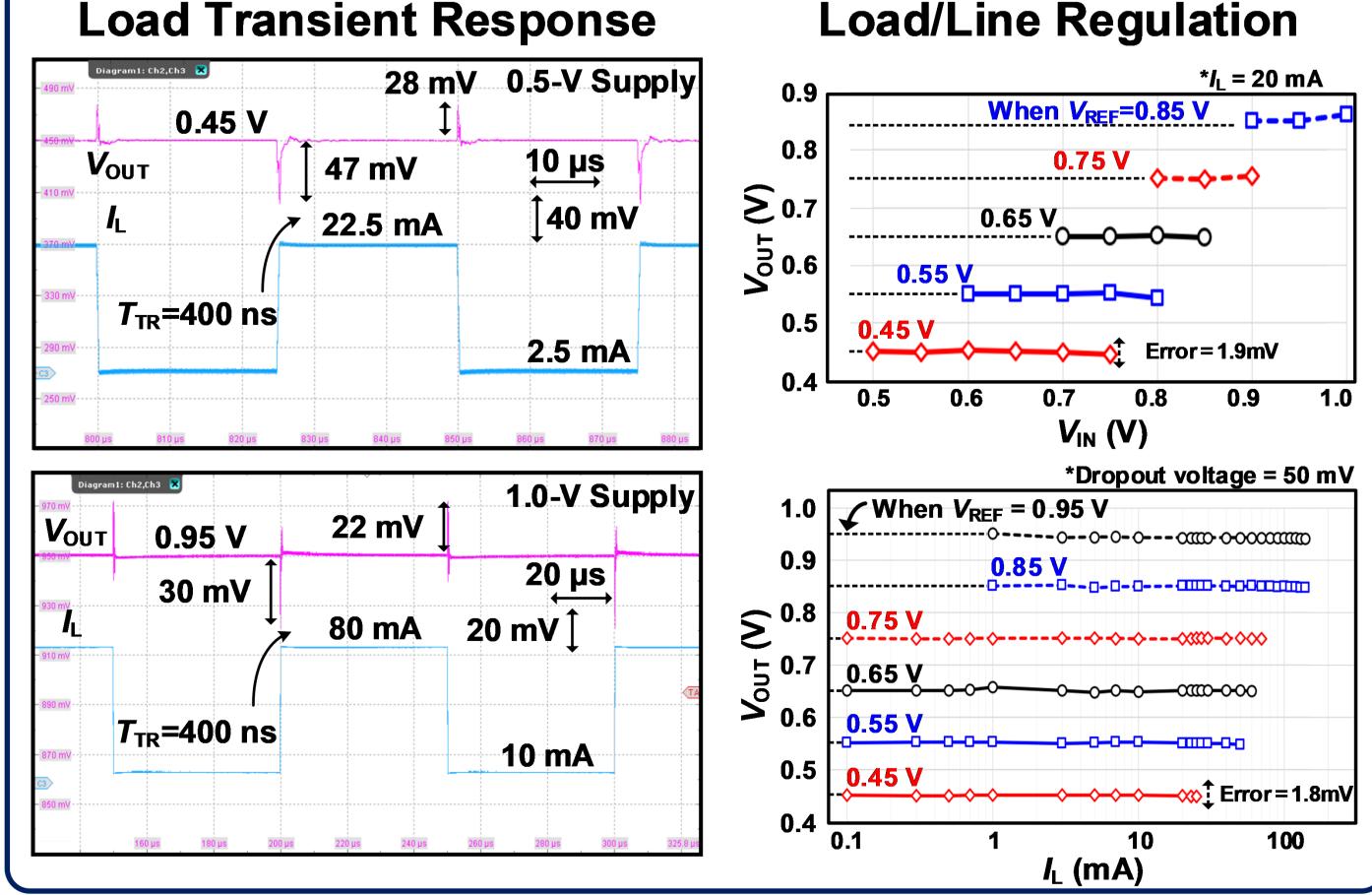

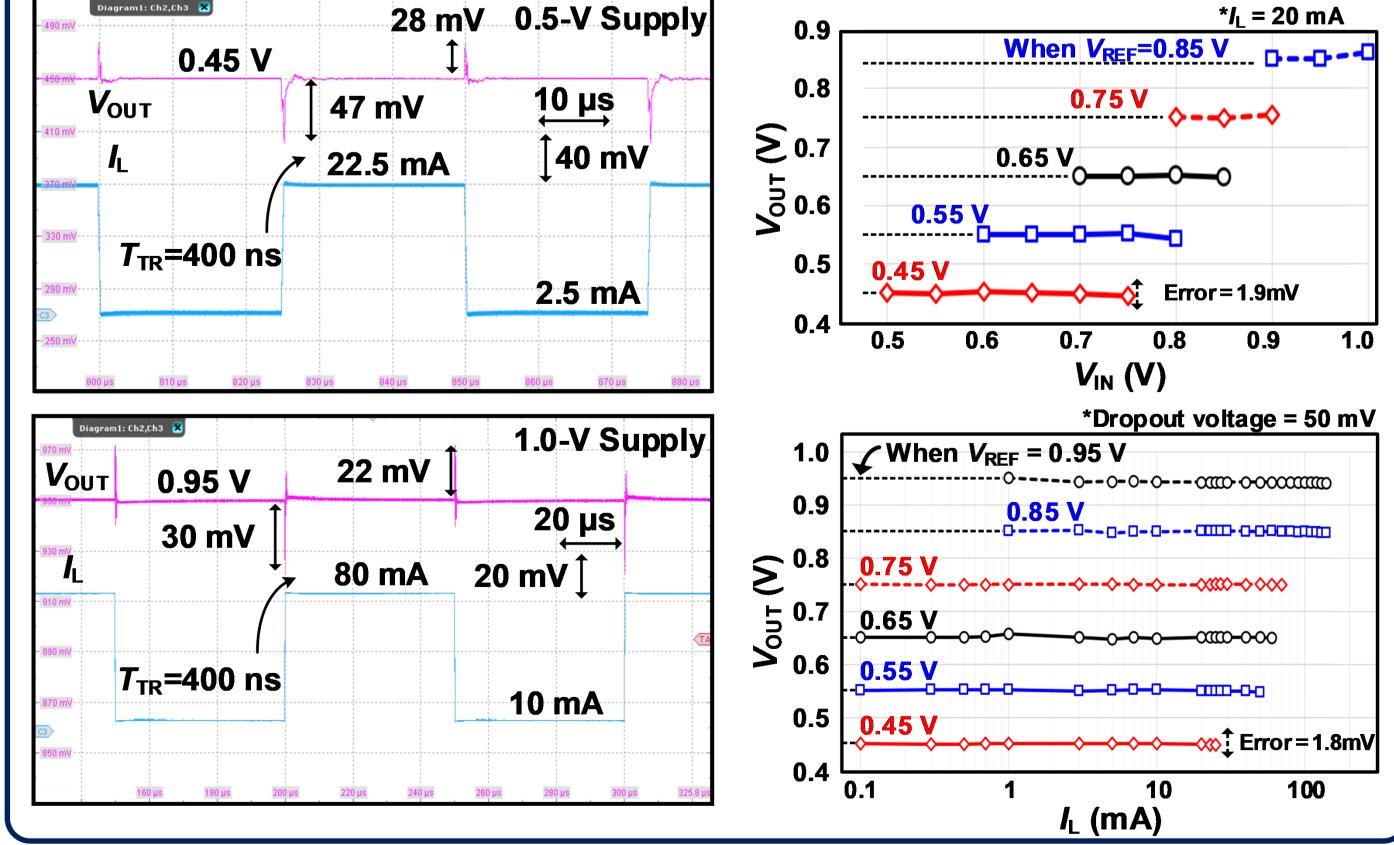

#### Measurement Transient & Regulation

|                                                 | This work     | ISSCC18[1]                                                                | ISSCC17[2]       | ISSCC17[3]       | ISSCC16[4]       |

|-------------------------------------------------|---------------|---------------------------------------------------------------------------|------------------|------------------|------------------|

| Process                                         | 65 nm         | 65 nm                                                                     | 65 nm            | 65 nm            | 28 nm            |

| Quantizer type                                  | SVER          | Replica VCO                                                               | Multi-bit<br>ADC | 1-bit<br>Compar. | Multi-bit<br>ADC |

| V <sub>IN</sub> (V)                             | 0.5 – 1.0     | 0.6 - 1.2                                                                 | 0.45 - 1.0       | 0.5 – 1.0        | 1.1              |

| <i>V</i> оит <b>(V)</b>                         | 0.45 - 0.95   | 0.4 – 1.1                                                                 | 0.4 - 0.95       | 0.3 - 0.45       | 0.9              |

| I <sub>L,MAX</sub> (mA)                         | 25            | 100                                                                       | 3.356            | 2                | 200              |

| С <sub>L</sub> (nF)                             | 0.1           | 0.04                                                                      | 0.1              | 0.4              | 23.5             |

| T <sub>SETTLE</sub> (μs)                        | 1.2           | 1.24                                                                      | 1.41             | 0.1              | 20               |

| Quiescent <i>I</i> <sub>Q</sub> (µA)            | 25 – 127      | 100 – 1070                                                                | 8.1 – 258        | 14               | NA               |

| ∆V <sub>OUT</sub> (mV)<br>@∆/ <sub>L</sub> (mA) | 47<br>@ 20    | 108<br>@ 50                                                               | 34<br>@ 1.44     | 40<br>@ 1.06     | 120<br>@ 180     |

| **FOM <sub>TR</sub> (ps)                        | 0.29          | 1.38                                                                      | 20               | 199.4            | 9.6              |

| Load regulation<br>(mV/mA)                      | 0.072         | 0.72*                                                                     | 2.5*             | < 5.6            | NA               |

| Area (mm²)                                      | 0.0488        | 0.0374                                                                    | 0.03             | 0.0023           | 0.021            |

| Estimated from me                               | easurement re | **FOM <sub>TR</sub> : $C_L \cdot \Delta V_{OUT} \cdot I_Q / \Delta I_L^2$ |                  |                  |                  |

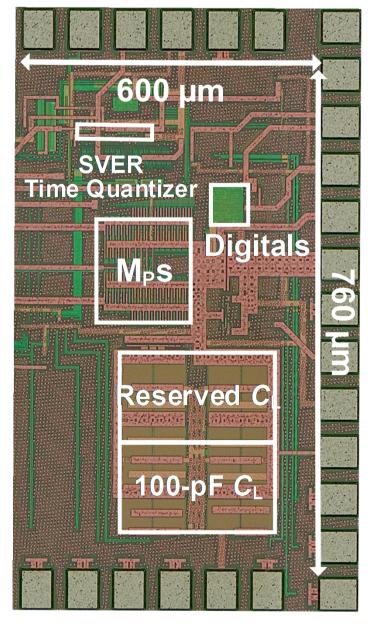

#### **Die Micrograph**

The smallest transient FOM and the best load regulation, while it used 0.5-V supply. And it had a small  $\Delta V_{OUT}$  by using SVER time quantizer

References [1] S. Kundu et al., ISSCC, pp. 308-310, Feb. 2018 [2] D. Kim et al., ISSCC, pp. 148-149, Feb. 2017. [3] L. Salem, et al., ISSCC, pp. 340–341, Feb. 2017. [4] Y. Lee et al., ISSCC, pp. 150-151, Feb. 2016.

Acknowledgement The chip fabrication and EDA tool were supported by the IC Design Education Center(IDEC), Korea.